并联谐振电路

当电源频率在电源电压和产生电阻电路的电流之间产生零相位差时,就会发生并联谐振

在许多方面,并联谐振电路与我们在前一个教程中看到的串联谐振电路完全相同。两者都是包含两个电抗元件的三元网络,使它们成为二阶电路,两者都受到电源频率变化的影响,并且两者都有一个频率点,它们的两个电抗元件相互抵消,影响电路的特性。两个电路都具有共振频率点。

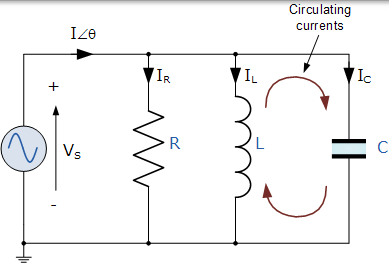

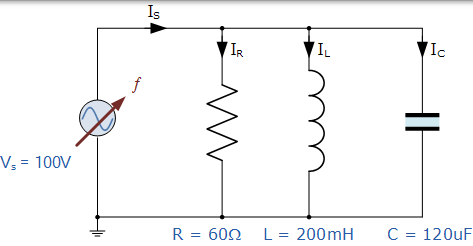

然而,这次的不同之处在于并联谐振电路受到流过并联 LC 谐振电路内的每个并联支路的电流的影响。甲储能电路是的并联组合大号和 C 了在滤波器网络用来选择或拒绝 AC 频率。考虑下面的并联 RLC 电路。

并联 RLC 电路

让我们定义一下我们对并联 RLC 电路的了解。

当通过并联组合的合成电流与电源电压同相时,包含电阻 R,电感,L 和电容 C 的并联电路将产生并联谐振 (也称为反谐振)电路。在谐振时,由于振荡的能量,在电感器和电容器之间将存在大的循环电流,然后并联电路产生电流谐振。

甲并联谐振电路中电感器和电容器的电场的磁场存储电路的能量。该能量不断地在电感器和电容器之间来回传递,这导致从电源汲取零电流和能量。

这是因为 IL 和 IC 的相应瞬时值总是相等且相反,因此从电源汲取的电流是这两个电流的矢量相加和流入 IR 的电流。

在交流并联谐振电路的解决方案中,我们知道电源电压对于所有分支都是通用的,因此可以将其作为我们的参考矢量。每个并联支路必须像串联电路一样单独处理,以便并联电路的总供电电流是各个支路电流的矢量相加。

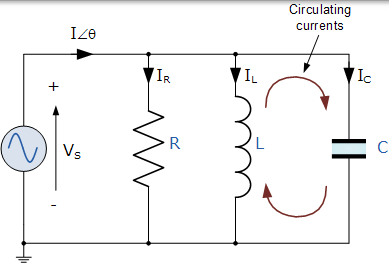

然后我们有两种方法可用于并联谐振电路的分析。我们可以计算每个分支中的电流然后加在一起或计算每个分支的导纳以找到总电流。

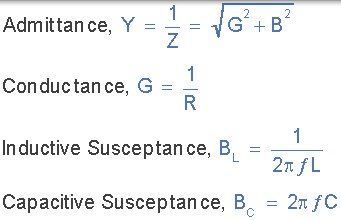

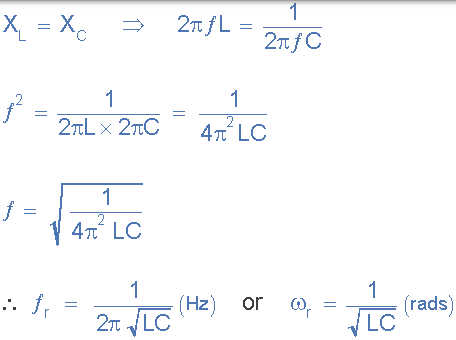

我们知道,从以前的串联谐振教程,发生谐振时,VL = -VC,这种情况发生在两个电抗相等,XL = XC。并联电路的准入如下:

当 XL = XC 并且 Y 的虚部变为零时发生共振。然后:

注意,在谐振时,并联电路产生与串联谐振电路相同的等式。因此,如果电感器或电容器并联或串联连接则没有区别。

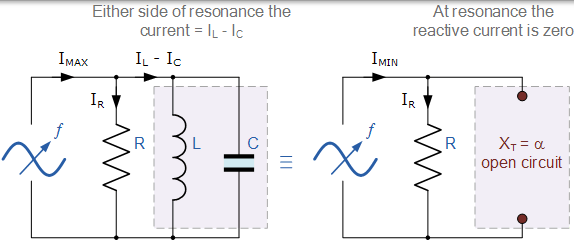

同样在谐振时,并联 LC 谐振电路的作用类似于开路,其中电路电流仅由电阻器 R 确定。因此,谐振时并联谐振电路的总阻抗变为电路中电阻的值,如图所示 Z = R.

因此,在谐振时,并联电路的阻抗处于其最大值并且等于电路的电阻,从而产生高电阻和低电流的电路条件。同样在谐振时,由于电路的阻抗现在只是电阻的阻抗,因此总电路电流 I 将与电源电压 VS “同相” 。

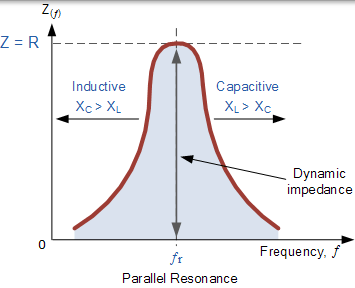

我们可以通过改变电阻值来改变电路的频率响应。如果 L 和 C 保持恒定,则改变 R 的值会影响在谐振时流过电路的电流量。然后,谐振 Z = RMAX 处的电路阻抗称为电路的“动态阻抗”。

并联谐振电路中的阻抗

注意,如果并联电路阻抗在谐振时最大,那么,电路导纳必须处于最小值,并联谐振电路的特性之一是导纳非常低,限制了电路电流。与串联谐振电路不同,并联谐振电路中的电阻器对电路带宽具有阻尼效应,使得电路选择性较低。

而且,由于电路电流对于任何阻抗值 Z 都是恒定的,并联谐振电路两端的电压将具有与总阻抗相同的形状,并且对于并联电路,电压波形通常取自电容器两端。

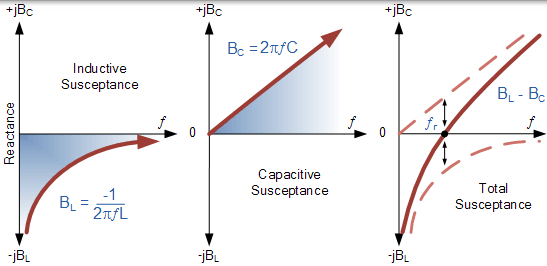

现在我们知道,在共振频率, ƒř 电路的导纳处于其最小值和等于电导,G ^ 由下式给出 1 / R,因为在并联谐振电路的导纳的虚数部分,即电纳,乙为零,因为 BL = BC,如图所示。

在共鸣中的继承

从上面,所述感纳,乙L 成反比如由双曲线表示的频率。的电容性电纳,乙C 是成正比的频率,并因此是由一条直线来表示。最终曲线显示了并联谐振电路的总电纳与频率的关系图,并且是两个电纳的差异。

然后我们可以看到,在谐振频率点,它穿过水平轴,总电路电纳为零。低于谐振频率点,感应电纳主导电路产生“滞后”功率因数,而高于谐振频率点,容性电纳主导产生“超前”功率因数。

因此,在谐振频率下,从电源汲取的电流必须与施加的电压“同相”,因为并联电路中只存在电阻,因此功率因数变为 1 或 1,( θ= 0o)。

此外,随着并联电路的阻抗随频率变化,这使得电路阻抗“动态”,而谐振电流与电压同相,因为电路的阻抗充当电阻。然后我们已经看到谐振时并联电路的阻抗等于电阻值,因此该值必须代表所示电路的最大动态阻抗( Zd)。

并联谐振电路中的电流

作为总纳是在共振频率为零时,导纳处于其最小值和等于电导,G ^ 。因此,在谐振流过电路的电流也必须处于其最小值作为电感性和电容分支电流相等( IL = IC ^)和 180o 异相。

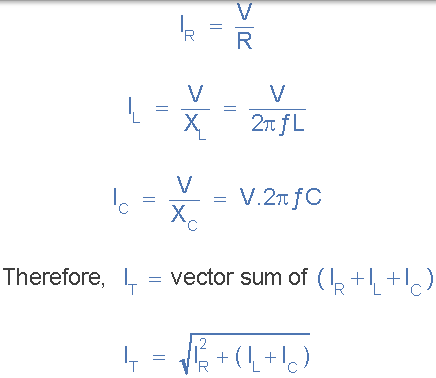

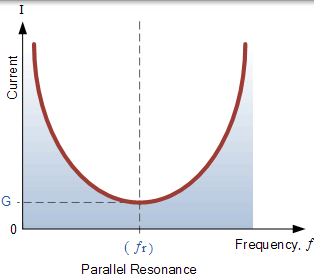

我们记得在并联 RLC 电路中流动的总电流等于各个支路电流的矢量和,并且对于给定频率,计算如下:

在谐振时,电流 IL 和 IC 相等并且抵消给出净无功电流等于零。然后在共振时,上述等式变为。

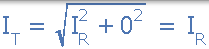

由于流过并联谐振电路的电流是电压除以阻抗的乘积,因此在阻抗谐振时,Z 处于其最大值( = R)。因此,该频率下的电路电流将处于其最小值 V / R,并且并联谐振电路的电流与频率的关系曲线如下所示。

共振时的并联电路电流

并联谐振电路的频率响应曲线显示电流的大小是频率的函数,并将其绘制在图表上,向我们显示响应从其最大值开始,在 IMIN = 时在谐振频率处达到其最小值 IR 然后再次增加到最大值,因为 ƒ 变为无限。

结果是,流过电感器 L 和电容器 C 槽电路的电流幅度可能比电源电流大很多倍,即使在谐振时也是如此,但它们是相等的并且相反(180o out-他们有效地相互取消了。

由于并联谐振电路仅在谐振频率上起作用,这种类型的电路也称为**抑制电路,**因为在谐振时,电路的阻抗处于其最大值,从而抑制或抑制其频率等于其谐振频率的电流。并联电路中的谐振效应也称为“电流谐振”。

上面用于定义并联谐振电路的计算和曲线图类似于我们用于串联电路的那些。然而,并联电路的特性和曲线图与串联电路的特性和曲线完全相反,并联电路的最大和最小阻抗,电流和放大倍数相反。这就是并联谐振电路也被称为反谐振电路的原因。

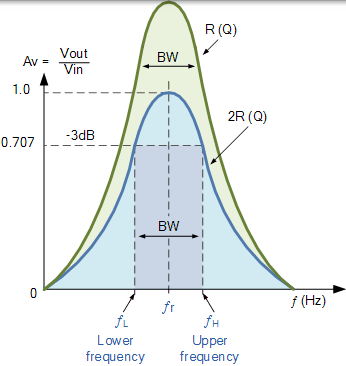

并联谐振电路的带宽和选择性

并联谐振电路的带宽以与串联谐振电路完全相同的方式定义。给出的上限和下限截止频率分别为: ƒ上部 和 ƒ下部 分别表示半功率频率,其中电路中消耗的功率是谐振频率 0.5(I2 R)下消耗的全功率的一半,这给了我们电流值相同的-3dB 点,等于其最大谐振值的 70.7%, (0.707 x I)2 R

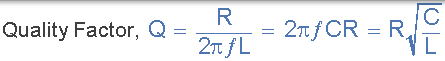

与串联电路一样,如果谐振频率保持不变,则品质因数 Q 的增加将导致带宽减小,同样,品质因数的降低将导致带宽增加,如下所定义:

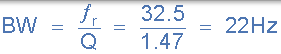

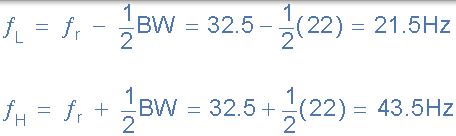

BW =ƒR / Q 或 BW =ƒ上 - ƒ下

同样改变电感器 L 和电容器之间的比率 C 或电阻值 R,带宽以及电路的频率响应将在固定的谐振频率下改变。该技术广泛用于无线电和电视发射机和接收机的调谐电路。

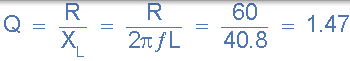

并联谐振电路的选择性或 Q 因子通常定义为循环支路电流与电源电流之比,如下:

注意,并联谐振电路的 Q 因子是串联电路的 Q 因子的表达式的倒数。同样在串联谐振电路中,Q 因子给出电路的电压放大率,而在并联电路中,它给出电流放大率。

并联谐振电路的带宽

并联共振示例 No1

由 60Ω 电阻,120uF 电容和 200mH 电感组成的并联谐振网络连接在正弦电源电压上,该电压在所有频率下具有 100 伏的恒定输出。计算电路的谐振频率,品质因数和带宽,谐振电路电流和电流放大倍数。

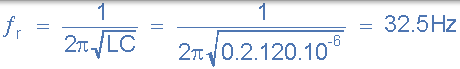

- 谐振频率, ƒř

- 共振时的感应电抗,XL.

- 品质因素,Q

- 带宽,BW

- 上下-3dB 频率点, ƒH 和 ƒL

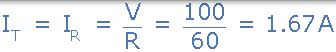

- 共振时的电路电流,IT.

在谐振时,电路的动态阻抗等于 R.

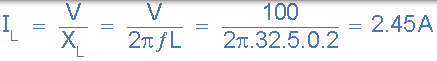

- 当前放大倍数,Imag

请注意,谐振时电源(电阻电流)的电流仅为 1.67 安培,而 LC 谐振电路周围的电流则为 2.45 安培。我们可以通过计算谐振时流经电感(或电容)的电流来检查该值。

并联共鸣教程摘要

我们已经看到并联谐振电路类似于串联谐振电路。当总电路电流与电源电压“同相”时,并联 RLC 电路中发生谐振,因为两个电抗元件相互抵消。

在谐振时,电路的导纳处于最小值并且等于电路的电导。同样在谐振时,从电源汲取的电流也是最小的,并且由并联电阻的值确定。

用于计算谐振频率点的等式对于先前的串联电路是相同的。然而,虽然在串联 RLC 电路中使用纯的或不纯的元件不会影响谐振频率的计算,但是在并联的 RLC 电路中它确实如此。

在本教程中关于并联谐振,我们假设两个无功分量是纯电感和纯电容,零阻抗。然而实际上,电感器将包含一些串联的电阻,RS 与其感应线圈,因为电感器(和螺线管)是缠绕的线圈,通常由铜制成,缠绕在中心芯上。

因此上述用于计算所述并联谐振频率的基本方程, ƒř 纯并联谐振电路将需要稍微修改以考虑具有串联电阻不纯电感器。

使用不纯电感的谐振频率

其中:L 是线圈的电感,C 是并联电容,RS 是线圈的直流电阻值。